لیتوگرافی ۳ و ۲ نانومتری TSMC بهترتیب در سال ۲۰۲۳ و ۲۰۲۵ از راه میرسند

شرکت تایوانی TSMC برنامه زمانی خود را برای توسعه فناوریهای ساخت تراشهها بر پایه لیتوگرافی ۲ و ۳ نانومتری منتشر کرد. این شرکت یکی از بزرگترین سازندگان تراشه در دنیاست.

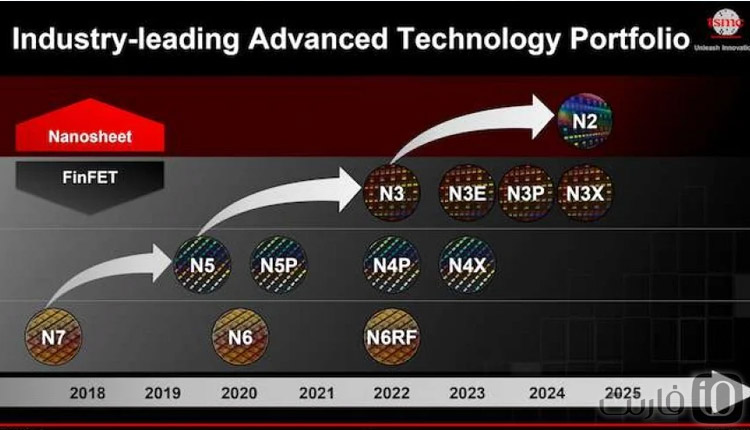

طبق این برنامه زمانی، TSMC فناوری ۳ نانومتری خود را در نیمه دوم امسال معرفی خواهد کرد و در سال ۲۰۲۵ نیز لیتوگرافی ۲ نانومتری خود را رونمایی خواهد کرد. این لیتوگرافی در ساخت پردازندهها و گرافیکهای بسیار پیشرفته مورد استفاده قرار خواهد گرفت.

لیتوگرافی ۳ نانومتری در مجموع شامل کلاسهای مختلفی به نامهای N3E ،N3P ،N3S و N3X خواهد بود و هر کدام از آنها قابلیتهای ویژهای را ارائه خواهند کرد. این نسخهها دارای بهبودهای قابلتوجهی در بخش عملکرد، تراکم ترانزیستورها و ولتاژ افزوده برای پردازشهای سنگین خواهند بود.

بهگفته TSMC، همه نسخههای فوق از معماری پیشرفته FINFLEX بهره خواهند برد که انعطافپذیری زیادی به آنها خواهد بخشید. این فناوری همچنین به طراحان تراشه اجازه خواهد داد تا عملکرد، مصرف انرژی و هزینه تراشههای خود را با استفاده از این معماری بهینهسازی کنند.

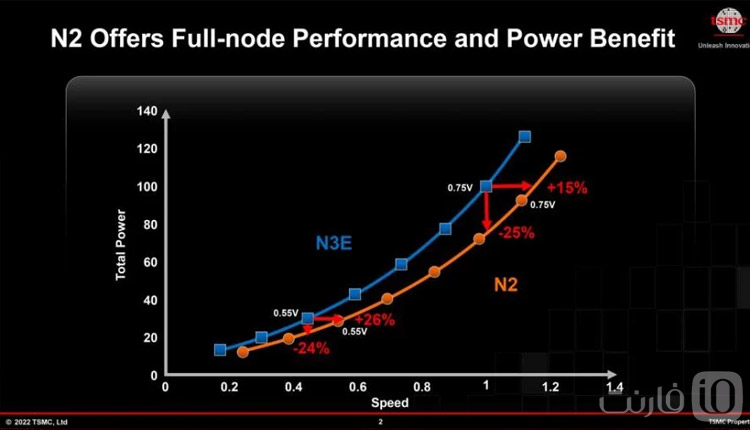

لیتوگرافی ۲ نانومتری TSMC نیز بهبودهای قابلتوجهی نسبت به فناوری ۳ نانومتری ارائه خواهد کرد. این لیتوگرافی حدود ۱۰ تا ۱۵ درصد افزایش سرعت و ۲۵ تا ۳۰ درصد کاهش مصرف انرژی را به ارمغان خواهد آورد.

این لیتوگرافی ظاهرا برای ارائه چنین بهبودهایی، از ترانزیستورهای GAAFET استفاده خواهد کرد و شامل نسخههای مختلفی برای کاربردهای مختلف خواهد بود.

طبق برنامه زمانی TSMC، تولید انبوه اولین تراشههای ساخته شده با لیتوگرافی 3 نانومتری این شرکت از ماههای آینده شروع خواهد شد و در فصل اول ۲۰۲۳ نیز شاهد عرضه آنها خواهیم بود. تولید تراشههای ۲ نانومتری هم از سال ۲۰۲۵ آغاز خواهد شد.